选择性钨沉积工艺解决晶体管微缩瓶颈

- 详细资料

- 分类:钨业新闻

- 发布于 2020年7月23日 星期四 16:29

- 作者:Zhenghua

- 点击数:1862

随着光刻技术的发展,晶体管导线通孔的微缩技术也面临一定的挑战。应用材料公司创新的选择性钨沉积工艺消除了在先进晶圆代工-随逻辑节点微缩而阻碍晶体管功率和性能的导线电阻瓶颈,为未来芯片的小型化、高效化发展,以及降低成本提供助力。

传统金属填充导线通孔一般通过多层工艺完成,包括通孔内壁涂覆氮化钛粘附阻挡层、成核层,以及电阻率低的钨金属填充层。在7nm晶圆代工节点,导线通孔直径只有20nm左右。粘附阻挡层和成核层约占通孔容积的75%,只剩25%左右的容积用于填钨。但是细钨丝电阻很高,使得芯片功率、性能和面积/成本(PPAC)的优化和进一步的2D尺寸微缩遭遇重大瓶颈。

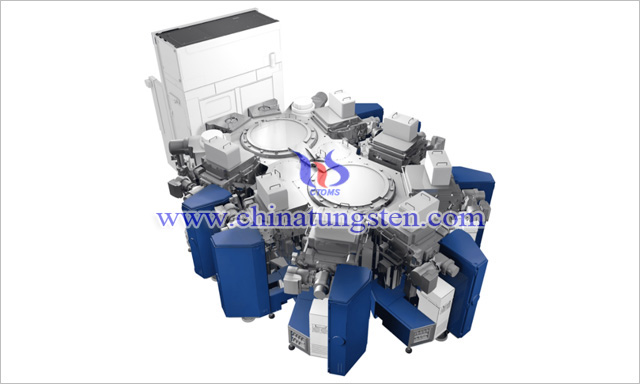

美国半导体设备供应商应用材料公司最新的选择性钨沉积系统(Endura® Volta™ Selective Tungsten CVD系统)可以克服传统晶体管连接方式的局限性。芯片制造商可以在晶体管导线通孔中选择性地进行钨沉积(只沉积电阻率较低的钨金属),完全不需要粘附阻挡层和成核层,从而解决微缩面临的瓶颈,可以将晶体管及其导线的节点继续微缩到5nm、3nm及以下,同时提升计算机芯片的连接速度。

据了解,该选择性钨沉积系统是一个集成材料解决方案,在一个清洁、高真空的环境中结合多种工艺进行。对晶圆进行原子级的表面处理并采取独特的沉积工艺,使得钨原子在通孔选择性沉积,实现无脱层、无缝隙、无空洞完美地自下而上填充。

半导体行业市场研究公司VLSI Research董事长兼首席执行官Dan Hutcheson表示,随着EUV到来,我们需要解决一些关键的材料工程挑战来延续2D微缩的发展,“在我们这个行业,粘附阻挡层就像医学里的‘动脉斑块’,它剥夺了芯片达到最佳性能所需的电子流。应用材料公司的选择性钨沉积是我们期待已久的突破。”

| 钨产品供应商:中钨在线科技有限公司 | 产品详情: http://cn.chinatungsten.com |

| 电话:0592-5129696 传真:5129797 | 电子邮件:sales@chinatungsten.com |

| 钨钼文库:http://i.chinatungsten.com | 钨钼图片: http://image.chinatungsten.com |

| 钨业协会:http://www.ctia.com.cn | 钼业新闻: http://news.molybdenum.com.cn |